› Forums › IoTStack › News (IoTStack) › The five technical challenges Cerebras overcame in building the first trillion-transistor chip – TechCrunch

- This topic has 1 voice and 0 replies.

-

AuthorPosts

-

-

November 1, 2019 at 6:15 am #35385

#News(IoTStack) [ via IoTGroup ]

Headings…

The five technical challenges Cerebras overcame in building the first trill

Going big means nothing but challenges

Entering uncharted territory in chip design

From theory to realityAuto extracted Text……

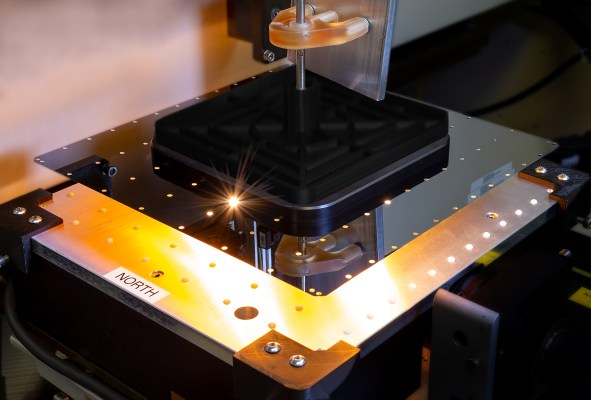

Fabs like TSMC take standard-sized silicon wafers and divide them into individual chips by using light to etch the transistors into the chi

p.

p.

Cerebras throws out the idea of etching a bunch of individual chips onto a single wafer in lieu of just using the whole wafer itself as one gigantic chip.

That allows all of those individual cores to connect with one another directly — vastly speeding up the critical feedback loops used in deep learning algorithms — but comes at the cost of huge manufacturing and design challenges to create and manage these chips.

The first challenge the team ran into, according to Feldman, was handling communication across the “scribe lines.” While Cerebras’ chip encompasses a full wafer, today’s lithography equipment still has to act like there are individual chips being etched into the silicon wafer.

So the company had to invent new techniques to allow each of those individual chips to communicate with each other across the whole wafer.

Cerebras approached the problem using redundancy by adding extra cores throughout the chip that would be used as backup in the event that an error appeared in that core’s neighborhood on the wafer.

Those first two challenges — communicating across the scribe lines between chips and handling yield — have flummoxed chip designers studying whole-wafer chips for decades.

And indeed, the toughest challenges, according to Feldman, for Cerebras were the next three, since no other chip designer had gotten past the scribe line communication and yield challenges to actually find what happened next.

There is a challenge though: Absolutely nothing on the market is designed to handle a whole-wafer chip.

“And so we have designed this whole manufacturing flow, because nobody has ever done it.” Cerebras’ technology is much more than just the chip it sells — it also includes all of the associated machinery required to actually manufacture and package those chips

Read More..

AutoTextExtraction by Working BoT using SmartNews 1.0299999999 Build 26 Aug 2019

-

-

AuthorPosts

- You must be logged in to reply to this topic.